WANTED: Individual or team to take over this project. I'm in my 70's and want to put my feet up. Contact details in footer.

| AS Level Logic Algebra Bistable Latch Karnaugh Maps Multiplexing NOR Array >Propagation Delay< |

Logic Propagation Delay |

|

A 4000 series CMOS gate might have a propagation delay of about 10 nanoseconds.

This is the time taken for the signal to get through the gate.

This time is sometimes called latency.

It depends on the load capacitance. This load has to be charged or discharged.

Smaller load capacitances lead to faster chips.

Even wires have a propagation delay.

This is because the signals travel at the speed of light or a bit slower on circuit boards.

Computer mother-board and other high speed digital designs have to take these delays into account.

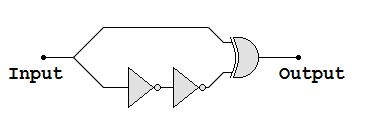

This circuit has two paths. The one with the extra NOT gates adds an extra 20 nanosecond delay. The XOR gate output will have a 20 nanosecond pulse output. Unwanted pulses like this are called GLITCHES. If you need a very short pulse, this circuit becomes useful.

With equal inputs, the XOR gate output should always be LOW. The two NOT gates cancel each other out so the XOR gate should always have equal inputs. This is almost true but the time delay leads to non-equal inputs for a few nanoseconds. This causes the glitch.

This simulation exagerates the propagation delay by adding large load capacitances. The glitch is very obvious.

Subject Name Level Topic Name Question Heading First Name Last Name Class ID User ID

|

Q: qNum of last_q Q ID: Question ID Score: num correct/num attempts Date Done

|

Question Text

image url

Help Link

Add Delete Clone Edit Hardness

Contact, Copyright, Cookies and Legalities: C Neil Bauers - reviseOmatic V4 - © 2016 to 2025

Hosted at Akamai Cloud - London

Please report website problems to Neil