WANTED: Individual or team to take over this project. I'm in my 70's and want to put my feet up. Contact details in footer.

| GCSE Sequential Logic BCD Counting D Type Flip Flop D Type Latch Decade Counter Sequencer >Up Counter< |

Sequential Logic Up Counter |

|

On the rising edge of the clock pulse, the input (D) is copied to the output (Q).

Since Q is connected to D, the output is inverted on the rising edge.

A ripple counter is an asynchronous counter where only the first flip-flop is clocked by an external pulse.

All subsequent flip-flops are clocked by the output of the preceding flip-flop.

The counter output might be momentarily wrong until the clock pulse has reached every the flip-flop.

This takes about 20 nanoseconds per flip-flop.

In decimal this counts 0 1 0 1 0 1 and in binary, it's the same.

View counter in the Lushprojects Simulator.

In decimal, this counter counts 0 1 2 3 0 1 2 3 0 1 2 3 and in binary, 00 01 10 11 00 01 10 11 00 01 10 11 00 01 10 11 .

View counter in the Lushprojects Simulator.

On the rising edge of the clock pulse, D is copied to Q.

Since NOT Q is connected to D, the data is inverted on each rising edge.

This has the effect of dividing the frequency by two.

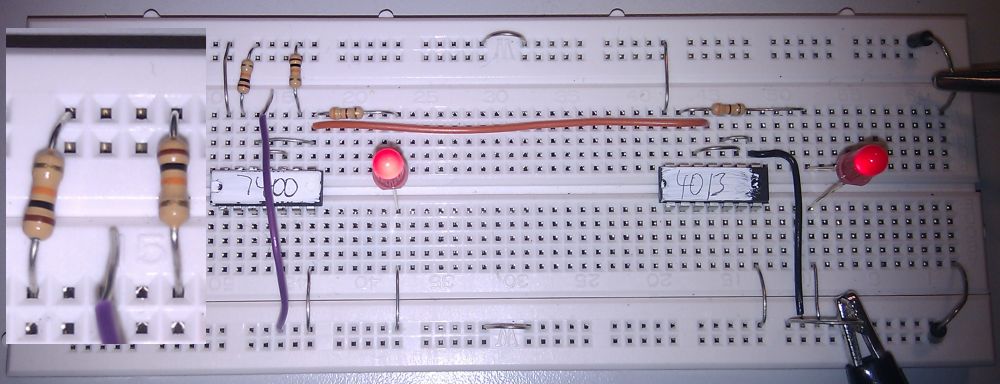

The two NAND gates are connected as a Bistable Flip Flop. This is used to debounce the switch pulses. The 4013 D Type Flip Flop is wired as a one bit binary counter. Each time the Bistable LED comes on (the rising edge), the counter LED changes state. This counter counts 0, 1, 0, 1, Etc.

This is a slightly odd circuit because two different families of logic chips are being used.

Subject Name Level Topic Name Question Heading First Name Last Name Class ID User ID

|

Q: qNum of last_q Q ID: Question ID Score: num correct/num attempts Date Done

|

Question Text

image url

Help Link

Add Delete Clone Edit Hardness

Contact, Copyright, Cookies and Legalities: C Neil Bauers - reviseOmatic V4 - © 2016 to 2026

Hosted at Akamai Cloud - London

Please report website problems to Neil